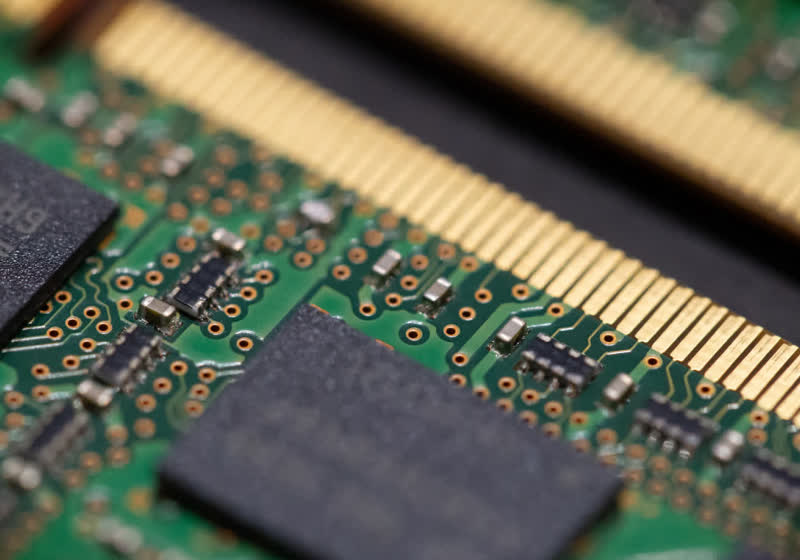

Taming the Tail: NoI Topology Synthesis for Mixed DL Workloads on Chiplet-Based Accelerators

NeutralArtificial Intelligence

A recent study discusses the challenges posed by heterogeneous chiplet-based systems, particularly focusing on the latency issues introduced by Network-on-Interposer (NoI) during large-model inference. As parameters and activations frequently shift between HBM and DRAM, this can lead to significant tail latency, impacting overall system performance. Understanding these dynamics is crucial for optimizing future chiplet designs and improving computational efficiency, especially as demand for high-performance computing continues to grow.

— Curated by the World Pulse Now AI Editorial System